番外篇-mipi dsi 协议

阅读 MIPI Alliance Standard for Display Serial Interface V1.0 不照搬全文,有部分个人理解,可能会有内容删减。

¶一、MIPI联盟显示系列接口的标准

显示串行接口 (DSI) 规范定义了主机处理器和外围设备之间的协议,这些协议符合 MIPI 联盟的移动设备接口规范。 DSI 规范建立在现有标准的基础上,采用了 MIPI 联盟标准中为 DBI-2 [2]、DPI-2 [3] 和 DCS [1] 定义的像素格式和命令集。

本规范规定了接口协议以及信号时序关系的描述,但没有规定电器规格和物理规格。此外此规范不包含 DPI-2 和 DBI-2 等传统接口。设备使用的辅助总线(i2c,spi等)本规范虽然不排斥,但也不包含在内。

显示串行接口(DSI)定义了外设与移动设备之间的高速串行接口,通常用于显示模块显示,例如 lcd 的的显示。通过这个接口可以提高设备的性能,降低设备的功耗,减少设备需要的引脚,同时提高可维护性和兼容性。

¶1、相关术语

“shall” 表示必须严格遵守的强制要求

“must” 仅用于描述不可避免的情况

“will” 仅仅用于陈述

“should” 表示在多种可能性中推荐一种比较合适的。

“may” 表示可能被允许

“can” 表示可以、等于、能够

¶1) 定义

Forward Direction(正向传输): 从发送时钟一侧到接收时钟一侧的传输,相对于高速串行时钟的方向定义的信号方向。

Half duplex(半双工): 在一条通道上进行双向数据传输,允许传输和接收,但一次只能在一个方向。

HS Transmission(高速传输): 在 HS 模式下正向发送一个或多个数据包。 HS 传输在数据包传输之前和之后由 LP-11 状态定界。

Host Processor(主机处理器): 提供移动设备核心功能的硬件和软件。

Lane: 由两组互补的差分通道组成,用于传输数据或时钟信号

Lane Interconnect: 用于差分高速信号和低功耗单端信号的双线点对点互连。

Lane Module: 用于在 lane 上发送或接受数据

Link(链路): 两个设备之间包含一个时钟通道和至少一个数据通道的完整连接。

LP Transmission(低功耗传输): 在 LP 模式或 Escape 模式中发送一个或多个数据包。 LP 传输在数据包传输之前和之后由 LP-11 状态分隔

Packet: 遵守一定协议的数据格式。字节是构成数据包的基本数据单位。

Payload: 仅应用数据——删除了所有链接同步、标头、ECC 和校验和以及其他与协议相关的信息。 这是主机处理器和外设之间传输的“核心”

PHY : 组成 lane 的物理链路

PHY Configuration(PHY配置): 一个 PHY 配置至少包含两个通道:一个时钟通道和一个或多个数据通道。

Reverse Direction: 反向是正向的相反方向。 请参阅Forward Direction 的说明。

Virtual Channel:(虚拟通道) 此规范支持最多四个外设的多个独立数据流。 每个外设的数据流是一个虚拟通道。 这些数据流可以交错并作为顺序数据包发送,每个数据包专用于特定的外围设备或通道。数据包协议包括将每个数据包定向到其预期外围设备的信息。

Word Count: 字节数

¶二、DSI Introduction

DSI 指定了主机处理器和显示模块等外围设备之间的接口。它通过采用 DPI-2、DBI-2 和 DCS 标准中指定的像素格式和命令集,以现有 MIPI 联盟标准为基础。下图显示了一个简化的 DSI 接口。从概念上来说,它像外围设备发送像素或者命令,并且可以从外围设备读回状态或像素信息。它和传统的区别在于它将所有像素数据,命令,和时间序列化打包发送。从而减少了控制信号等并行线。从系统或软件的角度来看,序列化和反序列化操作应该是透明的。最明显也不可避免的问题就是,将并行数据转换回串行数据会增加外设响应时间。使用帧缓冲可以降低这样的延时。

¶1、DSI Layer Definitions

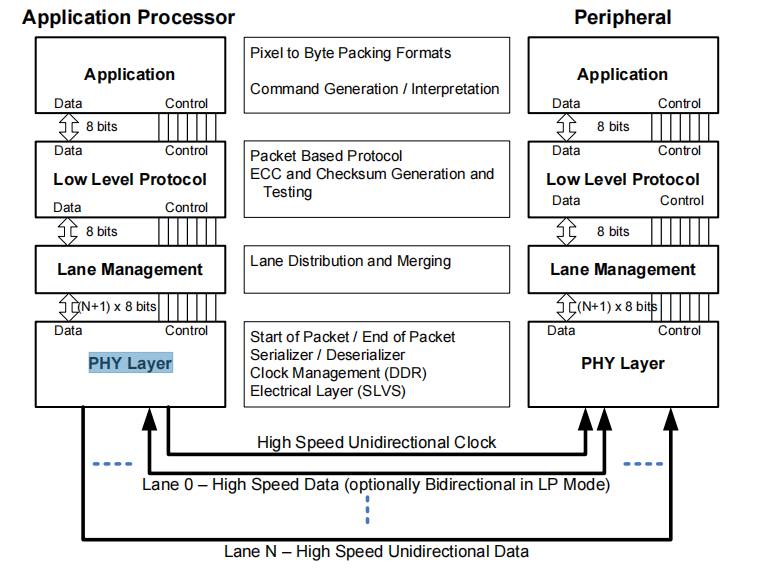

DSI 从概念上可以划分为以下几个功能层。

¶1)PHY Layer

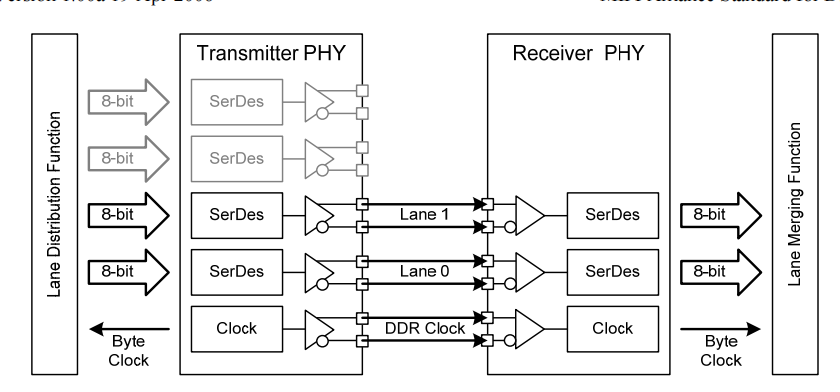

PHY 层指定了传输介质,输入输出电路,通信过程中 “1” 和 “0” 采取时机。它也指定了传输开始 SoT 和传输结束 EoT 的通信协议,其中也包括发送和接受的特定信息。位级和字节级同步机制作为 PHY 的一部分包含在内

¶2)Lane Management Layer

通道管理层(Lane Management Layer), 可以根据应用的需求,数据通道可以旋转1-4组lane,发送端该层则用于管理将数据分发到各个通道,接收端该该层将收到的信号进行组合恢复到原有的状态,即分发器功能与合并功能.

¶3) Protocol Layer

协议层(Low Level Protocol)规定了通过接口的位和字节的序列和值。 它指定如何将字节组织到称为数据包的定义组中。该协议定义了每个数据包所需的标头,以及如何生成和解释标头信息。 接口的发送端将报头和错误校验信息附加到正在发送的数据中。 在接收端,报头被剥离并由接收器中的相应逻辑解释。 错误检查信息可用于测试传入数据的完整性。 DSI 协议还记录了如何标记数据包以使用单个 DSI 将多个命令或数据流交织到不同的目的地。

¶4) Application Layer

应用层(Application Layer)该层描述了数据流中包含的数据的更高级别的编码和解释。 根据显示子系统架构,它可能由具有规定格式的像素或由显示模块内的显示控制器解释的命令组成。 DSI 规范描述了像素值、命令和命令参数到数据包组件中字节的映射.

¶2、Command and Video Modes

符合 DSI 的外设支持两种基本操作模式:Command Modes 和 Video Modes 。使用哪种模式取决于外设的架构和功能。模式定义反映了 DSI 用于显示互连的主要预期用途,但无意限制 DSI 在其他应用程序中运行。通常,外设既能进行命令模式操作也能进行视频模式操作。一些视频模式显示器还包括命令模式操作的简化形式,其中显示器可以从缩小尺寸或部分帧缓冲区刷新其屏幕,并且可以关闭与主机处理器的接口 (DSI) 以降低功耗

¶1) Command Mode

Command Mode 用于向外设发送数据和命令,例如包含显示控制器的外设,显示控制器可以包括本地寄存器和帧缓冲器。系统使用 Command Mode 读写寄存器和 frame buffer memory. 处理器通过向显示控制器发送命令、参数和数据来间接控制外设的活动。处理器还可以读取显示模块状态信息或帧存储器的内容.Command Mode 需要双向接口。

¶2) Video Mode Operation

Video Mode 指以实时像素流的形式从处理器传输到外围设备的操作。在正常操作中,显示模块依赖主机处理器以足够的带宽提供图像数据,以避免显示图像中出现闪烁或其他可见伪影。

一些 Video Mode 架构可能包括一个简单的时序控制器和部分帧缓冲器,用于在待机或低功耗模式下保持部分屏幕或较低分辨率的图像。这允许关闭接口以降低功耗。

为了降低复杂性和成本,仅在视频模式下运行的系统可以使用单向数据路径。

¶3) Virtual Channel Capability

用于支持多个显示器同时显示,DSI 允许多达 4 个虚拟通道,使多个外设的流量能够共享一个公共 DSI 链路。在一些高分辨率显示器设计中,多个物理驱动器服务于普通显示面板的不同区域。每个驱动程序都与自己的显示控制器集成在一起,该控制器通过 DSI 连接到主机处理器。使用虚拟通道,显示控制器将数据定向到各个驱动程序,无需多个接口或复杂的多路复用方案。

¶三、DSI Physical Layer

本节简要概述了DSI中使用的物理层,处理器和外设使用使用 clock + 一个或多个串行数据线来传输信息。通过总线发送高速串行数据的行为叫做 HS transmission 或者 burst

D-PHY 低级协议规定最小数据单位为一个字节,一次传输包含整数个字节

¶1、Data Flow Control

协议层和 PHY 层之间没有握手,允许协议层在传输进行时限制进出 PHY 层的数据传输。 数据包的发送和接收应完整无间断。 链路两端的协议层和数据缓冲应始终具有等于或大于 PHY 层电路的带宽。 一个实际的结果是系统实现者应该确保接收器的带宽能力等于或大于发射器的带宽能力。

¶2、Bidirectionality and Low Power Signaling Policy

DSI 实现的物理层由一到四个数据通道和一个时钟通道组成。 在 Command Mode 系统中,数据 lane 0 应该是双向的; 其他的数据 lane 应该是单向的。 在 Video Mode 系统中,数据 lane 0 可以是双向的或单向的;其他的数据 lane 应该是单向的。 有关详细信息,请参阅第 3 和 4 节。对于这两种接口类型,时钟通道只能由主处理器驱动,而不能由外设驱动。

正向的低功率传输应该使用数据 lane 0,数据 lane 0 上的反向传输应使用 Low Power Mode。外围设备应能够在 Low Power Mode 或 High Speed Mode 下接收任何传输。 请注意,在 LP 模式下传输时,传输带宽会大大减少。

对于双向通道,应仅使用低功耗 (LP) 模式在外设到处理器或反向传输数据。 有关不同传输模式的详细信息,请参阅 D-PHY 的 MIPI 联盟标准 [4]。

PHY 和协议层之间的接口有几个控制总线方向的信号。 当主机发送器需要来自外设的响应时,例如 返回 READ 数据或状态信息,它在传输的最后一个数据包期间向其 PHY 报告 TurnRequest。 这告诉 PHY 层在 EoT 序列之后声明总线转向 (BTA) 命令。

当外设接收到 Bus Turn-Around 命令时,其 PHY 层将 TurnRequest 响应为协议层的输入。 这告诉接收协议层它应该准备向处理器发送响应。 通常,刚接收到的数据包会告诉协议层一旦总线可用于传输到处理器时要发送什么信息。

在发送其响应后,外设类似地使用 TurnRequest 将总线控制权交还给处理器到其自己的 PHY 层。

¶3、Command Mode Interfaces

在 Command Mode 下运行的 DSI 处理器的最低物理层要求是:

- Data Lane Module: CIL-MUYY (HS-TX, LP-TX, LP-RX, and LP-CD)

- Clock Lane Module: CIL-MCNN (HS-TX, LP-TX)

在命令模式下运行的 DSI 外设的最低物理层要求是:

- Data Lane Module: CIL-SUYY (HS-RX, LP-RX, LP-TX, and LP-CD)

- Clock Lane Module: CIL-SCNN (HS-RX, LP-RX)

双向链路应支持反向 Escape Mode 和正向 Escape Mode

¶4、Video Mode Interfaces

在 Video Mode 下运行的 DSI 发射机的最低物理层要求是:

- Data Lane Module: CIL-MUNN (HS-TX, LP-TX)

- Clock Lane Module: CIL-MCNN (HS-TX, LP-TX)

在 Video Mode 下运行的 DSI 接收器的最低物理层要求是:

- Data Lane Module: CIL-SUNN (HS-RX, LP-RX)

- Data Lane Module: CIL-SUNN (HS-RX, LP-RX)

所有 DSI 实现都应支持所有数据 lane 上的 forward escape ULPM

¶5、Bidirectional Control Mechanism

总线转向由 token-passing 机制控制:主机处理器发送 Bus Turn- Around (BTA) 请求,该请求向外设传达其释放或停止驱动数据路径的意图,在此之后外设可以传输数据路径一个或多个数据包返回到主机处理器。

¶6、Clock Management

DSI 时钟是从主机处理器到外设的信号。 在某些系统中,它可能具有多种功能:

DSI Bit Clock:在整个链路中,DSI 时钟用作源同步位时钟,用于在接收器 PHY 中捕获串行数据位。 在传输数据时,该时钟应处于活动状态。

Byte Clock: 利用 DSI时钟在协议层和应用层之间生成的时钟,在 HS 传输过程中,每个字节的数据都伴随着一个字节时钟。

Application Clock(s): DSI Bit Clock 的分频版本可用于外设的其他时钟功能。这些“应用时钟”可能需要在没有串行数据传输时运行,或者它们可能需要持续运行(连续时钟)以支持外设的活动电路。例如:一些 mipi 转 rgb ic 可能会用到这个时钟。

对于连续时钟行为,时钟通道保持高速模式,在 HS 数据包传输之间生成活动时钟信号。 对于非连续时钟行为,时钟通道在 HS 数据包传输之间进入 LP-11 状态。

¶7、Clock Requirements

所有 DSI 发送器和接收器都应支持时钟通道上的连续时钟行为,并可选择支持非连续时钟行为。 DSI 处理器应支持需要它的系统的连续时钟,并具有关闭串行时钟的能力以降低功耗。

请注意,处理器控制所需的时钟操作模式,主机协议和应用程序控制 Clock Lane 操作模式(High Speed or Low Power mode). 系统设计人员负责了解连接到 DSI 的外设的时钟要求,并根据这些要求控制时钟行为。

请注意,在低功耗信号模式下,LP 时钟在功能上嵌入在数据信号中。 当 LP 数据传输结束时,时钟有效地停止并且后续的 LP 时钟不可用于外设。 如果外设需要额外的时钟来推进其逻辑状态、通过顺序缓冲区或类似方式移动数据,则可能需要向 LP 传输添加“虚拟”数据字节以影响状态机的前进进程或推进数据 通过时序逻辑。

BTA 的握手过程只允许主机处理器和外设之间的 Escape Mode 时钟频率存在有限的不匹配。处理器和外设之间的 Escape Mode 频率比不得超过 3:2。处理器负责控制自己的时钟频率以匹配外设。处理器 LP 时钟频率应在外围 LP 时钟频率的 67% 到 150% 的范围内。因此,外设实现者应指定外设的标称 LP 时钟频率和保证精度。

¶8、Clock Power and Timing

D-PHY 的 MIPI 联盟标准 [4] 中的附加时序要求指定了数据信号的功率状态和时钟信号的功率状态之间的时序关系。 主机处理器有责任观察这种时序关系。 如果 DSI 时钟连续运行,则这些时序要求不适用。

¶四、Multi-Lane Distribution and Merging

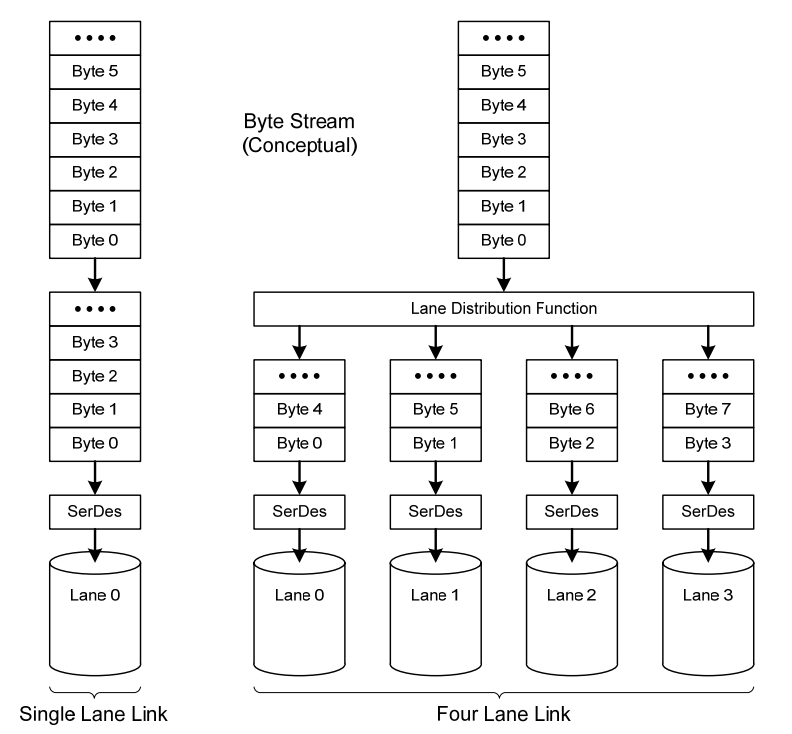

DSI 是一种通道可扩展的规范。 需要比一个数据通道提供更多带宽的应用程序可以将数据路径扩展到两个、三个或四个通道的宽度,并在峰值总线带宽上获得近似线性的增长。 该规范明确记录了应用程序数据和串行位流之间的映射,以确保使用多个通道的主机处理器和外设之间的兼容性。

多通道实现应使用单个公共时钟信号,由所有数据通道共享。

从概念上讲,PHY 和更高功能块之间是一个支持多通道操作的层。 在发送器中,如图 4 所示,该层在 N 条通道上分配一个数据包字节序列,其中每个通道都是一个独立的逻辑块和接口电路。 在接收器中,如图 5 所示,该层收集来自 N 个通道的传入字节,并将这些字节合并为完整的数据包,以传递到以下数据包分解器中。

Lane Distributor 接受任意字节长度的 HS 传输,缓冲 N 个字节,其中 N 是接口中实现的 Lanes 的数量,并在 N 个 Lanes 上并行发送 N 个字节的组。 在发送数据之前,所有通道并行执行 SoT 序列,以向其相应的接收单元指示数据包的第一个字节开始。 在 SoT 之后,车道从第一个数据包开始并行发送一组 N 个字节,遵循循环过程。 例如,对于双通道系统,数据包的字节 0 进入通道 0,字节 1 进入通道 1,字节 2 进入通道 0,字节 3 进入通道 1,依此类推。

¶1、Multi-Lane Interoperability and Lane-number Mismatch

使用的通道数应为静态参数。 它应在系统设计或初始配置时固定,不得动态更改。 通常,外设的带宽要求及其相应的通道配置确定了系统中使用的通道数。

处理器应配置为支持外设所需的相同通道数。 具体而言,具有 N-Lane 能力 (N > 1) 的处理器应能够使用较少的通道进行操作,以确保与具有 M 通道的外围设备的互操作性,其中 N > M。

¶1) Clock Considerations with Multi-Lane

在 EoT,协议层应根据最后一个活动通道模块的时序要求对公共 DSI 时钟信号进行控制。 如果协议层将 DSI 时钟置于 HS 传输之间的 LPS 中以节省功率,则它应遵守 DSI 时钟相对于 EoT 序列期间所有串行数据信号的时序要求.在 SoT 之前,应同样遵守与所有串行数据信号相关的 DSI 时钟启动的时序要求。

¶2) Bi-directionality and Multi-Lane Capability

外设通常对将数据返回到主机处理器没有大量的带宽要求。 为了保持设计简单并提高互操作性,所有符合 DSI 的系统都只能在 LP 模式下使用通道 0 将数据从外设返回到主机处理器。

¶3) SoT and EoT in Multi-Lane Configurations

由于 HS 传输由任意数量的字节组成,这些字节可能不是通道数的整数倍,因此某些通道可能会先于其他通道用完数据。 因此,Lane Management layer 在缓冲最后一组少于 N 个字节时,将其“有效数据”信号无效到所有没有进一步数据的通道中。

尽管所有 Lanes 都同时以并行 SoT 启动,但每个 Lane 独立运行,并且可能在其他 Lanes 之前完成 HS 传输,提前一个周期(字节)发送 EoT。

Link 接收端的 N 个 PHY 并行收集字节并将它们馈送到 Lane Management layer。 Lane Management layer 重建传输中的原始字节序列。图 7 和图 8 说明了 HS 传输可以针对不同通道数和数据包长度终止的各种方式。

注意多通道实现的特殊情况,有 N 个通道,它可能偶尔发送一个短的 HS 传输,其中数据包长度小于 N。在这种情况下,没有要传输的数据的通道应保留在 LPS 中

¶五、DSI Protocol

在 DSI 链路的发射机侧,并行数据、信号事件和命令在协议层转换为数据包,遵循本节中记录的数据包组织。 协议层附加数据包协议信息和报头,然后通过通道管理层向 PHY 发送完整的字节。 数据包由 PHY 序列化并通过串行链路发送。 DSI 链路的接收端执行与发送端相反的操作,将数据包分解为并行数据、信号事件和命令。

如果有多个通道,通道管理层会将字节分配到单独的 PHY,每个通道一个 PHY,如第 6 节所述。数据包协议和格式与所使用的通道数量无关。

¶1、Multiple Packets per Transmission

第一种是单独传输,一次传输可能包含一个数据包。但是这种情况如果要传输许多数据包并且据包分开发送,LPS 和高速模式之间频繁切换的开销将严重限制带宽。

第二种是单次传输,一次传输多个数据,DSI 协议允许连接多个数据包,这大大提高了有效带宽。这对于外设初始化等事件很有用,在这些事件中,许多寄存器可能会在系统启动时加载单独的写命令。图 9 说明了单独发送的多个数据包,并在单个 HS 传输中作为串联数据包发送。

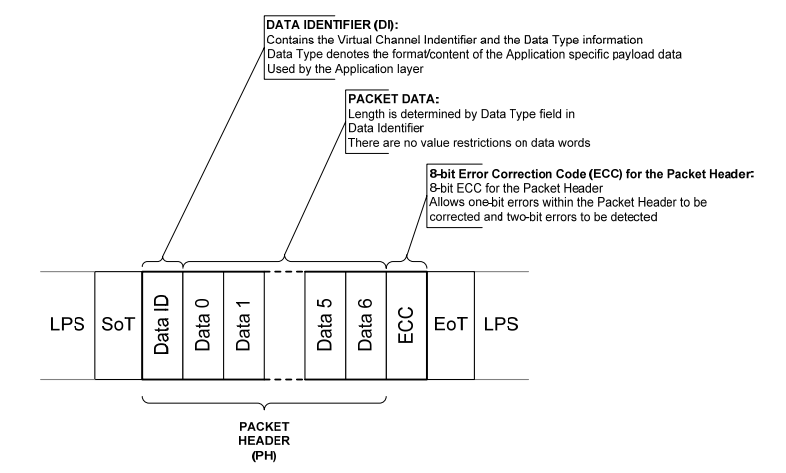

¶2、Packet Composition

数据包的第一个字节,即数据标识符 (DI),包括指定数据包长度的信息。 例如,在显示应用中的视频模式系统中,数据包的逻辑单元可以是一条水平显示线。 命令模式系统发送命令和相关参数集,参数数量取决于命令类型。数据包的大小可分为两类:

短数据包使用数据类型字段指定有效传送数据,长度为 2 到 9 个字节。有关有效传送数据,请参见表 16 和表 18。大多数命令模式命令和相关参数都使用短数据包。其他短数据包传达事件,如 H Sync 和 V Sync 。因为它们是短数据包,所以它们可以将准确的时序信息传送到外设的逻辑。

长数据包使用两字节字数字段指定有效传送数据。 有效传送数据的长度可以从 0 到 216 - 1 个字节。 因此,一个 Long 数据包的长度可能高达 65,541 字节。 长数据包允许传输大块的像素或其他数据。

命令模式操作的一个特例是视频速率(更新)流,它采用传输到外围设备的任意长的像素或其他数据流的形式。 由于所有 DSI 事务都使用数据包,因此视频流应分解为单独的数据包。 这种“打包”可以通过硬件或软件来完成。 然后外围设备可以将数据包重新组合成连续的视频流以供显示。

Set Maximum Return Packet Size 命令允许主机处理器限制来自外设的响应数据包的大小。 有关命令的说明,请参阅第 8.8.8.3 节。

¶3、Endian Policy

所有分组数据都以字节形式穿过接口。 按顺序,发送器应先发送数据 LSB,最后发送MSB。 对于具有多字节字段的数据包,除非在数据包定义中指明,最低有效字节应首先传输。

¶4、General Packet Structure

为低级协议通信定义了两种数据包结构:长数据包和短数据包。 对于这两种数据包结构,数据标识符始终是数据包的第一个字节。

¶1) Long Packet Format

长数据包由 32 位数据包头 (PH)、具有可变字节数的有效传送数据和 16 位数据包尾 (PF)。

数据包头 (PH):

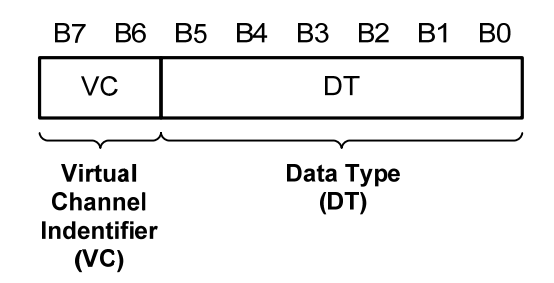

- 数据标识符(DI)1byte:含虚拟数据通道VC[7:6]和数据类型DT[5:0]

- 字节数(WC)2 byte:要传送的数据,长度固定两个字节

- 误差校正码(ECC)1byte:可以把一个位的错误纠正

有效传送数据:

- 6 ~ 65541 bytes 可变数据长度,最大字节 = 2^16

数据包页脚(2 byte):

- 用于校验

数据标识符定义了数据的虚拟通道和具有可变字节数的有效传送数据。 有关数据类型的说明,请参阅第 8.8 至 8.10 节

字数定义了有效传送数据中从包头结束到包尾开始之间的字节数。 包头和包尾均不应包含在字数统计中。

纠错码 (ECC) 字节允许在包头中纠正单比特错误和检测 2 比特错误。 这包括数据标识符和字数统计字段。

一旦接收器读取了有效传送数据,它就会读取数据包页脚中的校验和。 主机处理器应始终在数据包页脚中计算和传输校验和。 计算校验和不需要外设。 还要注意零字节有效传送数据的特殊情况:如果有效载荷的长度为 0,则校验和计算结果为 (FFFFh)。 如果未计算校验和,则数据包页脚将由两个全零字节 (0000h) 组成。 有关计算校验和的更多信息,请参见第 9 节。

在一般情况下,有效传送数据的长度应为字节的倍数。 此外,每种数据格式都可能对有效传送数据的长度施加额外的限制,例如 四个字节的倍数。

每个字节应首先传输最低有效位。 有效传送数据可以以仅受数据格式要求限制的任何字节顺序传输。 字数和校验和等多字节元素应首先传输最低有效字节。

¶2) Short Packet Format

短数据包:4byte 固定长度,主要用于传输命令,读写寄存器

- 数据标识符(DI) 1byte:含虚拟数据通道[7:6]和数据类型[5:0]

- 数据包 2byte: 要传送的数据

- 误差校正码(CEE) 1byte: 可以把一个位的错误纠正

¶5、Common Packet Elements

描述长包和短包的共有元素

¶1) Data Identifier Byte

任何数据包的第一个字节是 DI(数据标识符)字节。 图 12 显示了数据标识符 (DI) 字节的组成。

DI[7:6]: 这两个位识别指向四个虚拟通道中的一个的数据。

一个处理器可以使用标记命令或数据块为多达四个外设提供服务,使用针对不同外设的数据包的报头的虚拟通道 ID 字段。 虚拟通道 ID 通过将数据包复用到公共传输通道上,使一个串行流能够为两个或多个虚拟外设提供服务。 请注意,在单个传输中发送的数据包每个都有自己的虚拟通道分配,并且可以定向到不同的外围设备。 尽管 DSI 协议允许与多个外设进行通信,但该规范仅涉及主机处理器与单个外设的连接。 连接到多个物理外围设备的实现细节超出了本文档的范围。

DI[5:0]: 这六个位指定了数据类型。

数据类型字段指定了数据包内容的大小、格式以及在某些情况下的解释。 例如,在最小情况下,DT 字段是数据包内容。 通过指定数据包大小,它通知接收者在数据包的剩余部分中预期有多少字节。 这是必要的,因为没有特殊的数据包开始/结束同步代码来指示数据包的开始和结束。 这允许数据包传送任意数据,但它也需要数据包头来明确指定数据包的大小。 当接收逻辑倒计时到数据包结束时,它应假定下一个数据要么是新数据包的标头,要么是 EoT(传输结束)序列。

Virtual Channel Identifier – VC field, DI[7:6]

¶2) Error Correction Code

纠错码允许在包头中纠正单比特错误和检测 2 比特错误。 主机处理器应始终计算并传输 ECC 字节。 计算 ECC 字节不需要外设。 如果不使用 ECC,则应传输一个全零 (00h) 的字节。

¶6、Interleaved Data Streams

多通道的一种应用是在单个显示模块上使用两个或多个独立驱动器 IC 的高分辨率显示器。 每个驱动器 IC 仅寻址显示设备上的一部分列。 每个驱动程序 IC 仅捕获并显示针对该驱动程序的数据包内容,而忽略其他数据包。 参见图 14。

¶1) Interleaved Data Streams and Bi-directionality

当多个外设具有双向功能时,应有一种清晰明确的方法将 READ 数据、事件和状态从预期外设返回到主机处理器。 BTA 和虚拟通道 ID 的组合确保不会混淆期望哪个外设响应来自外设的任何请求。

双向性的结果是来自主机处理器的任何传输都不得包含超过一个需要外设响应的数据包。 无论通过链路连接到主机处理器的外设数量如何,这都适用。

¶7、Processor to Peripheral Direction (Processor-Sourced) Packet Data Types

| Data Type, Hex | Data Type, binary | Description | Packet Size |

|---|---|---|---|

| 0x01 | 00 00001 | Sync Event, V Sync Start | Short |

| 0x11 | 01 0001 | Sync Event, V Sync End | Short |

| 0x21 | 10 0001 | Sync Event, H Sync Start | Short |

| 0x31 | 11 0001 | Sync Event, H Sync End | Short |

| 0x02 | 00 0010 | Color Mode(CM) Off Command | Short |

| 0x12 | 01 0010 | Color Mode(CM) On Command | Short |

| 0x22 | 10 0010 | Shut Down Peripheral Command | Short |

| 0x32 | 11 0010 | Turn On Peripheral Command | Short |

| x3h and xBh | xx x011 | TGeneric WRITE, 0-7 parameters, bits 5:3 = parameter count | Short |

| x4h and xCh | xx x100 | Generic READ, 0-7 parameters, bits 5:3 = parameter count | Short |

| x5h and xDh | xx x101DCS WRITE, 0-6 parameters, bits 5:3 = parameter count + 1 | Short | |

| 0x06 | 00 0110 | DCS READ, no parameters | Short |

| 0x37 | 00 0110 | Set Maximum Return Packet Size | Short |

| 0x09 | 00 1001 | Null Packet, no data | Short |

| 0x19 | 01 1001 | Blanking Packet, no data | Short |

| 0x29 | 10 1001 | Generic Non-image Packet | Short |

| 0x39 | 11 1001 | DCS Long Write/write_LUT Command Packet | Short |

| 0x0E | 00 1110 | Packed Pixel Stream, 16-bit RGB, 5-6-5 Format | Short |

| 0x1E | 01 1110 | Packed Pixel Stream, 18-bit RGB, 6-6-6 Format | Short |

| 0x2E | 10 1110 | Loosely Packed Pixel Stream, 18-bit RGB, 6-6-6 Format | Short |

| 0x3E | 11 1110 | Packed Pixel Stream, 24-bit RGB, 8-8-8 Format | Short |

| x0h and xFh, unspecified | xx 0000xx 1111 | DO NOT USEAll unspecified codes are reserved | Short |

¶8、Processor-to-Peripheral Transactions – Detailed Format Description

¶1) Sync Event (H Start, H End, V Start, V End), Data Type = xx 0001 (x1h)

同步事件是两字节的数据包(一个命令字节,一个 ECC 字节),因此可以在时间上准确地表示同步脉冲的开始和结束等事件。 由于“开始”和“结束”是独立且不同的事件,同步脉冲的长度以及相对于活动像素数据的位置,前后肩延时可准确传达至外设。同步事件定义如下:

- Data Type = 00 0001 (01h) V Sync Start

- Data Type = 01 0001 (11h) V Sync End

- Data Type = 10 0001 (21h) H Sync Start

- Data Type = 11 0001 (31h) H Sync End

为了尽可能准确地表示时序信息,V Sync Start 事件表示 VSA 的开始,并且还暗示 VSA 第一行的 H Sync Start 事件。 类似地,V Sync End 事件意味着 VSA 最后一行的 H Sync Start 事件。

如果需要传送准确的脉冲长度信息,同步事件应该成对发生,即同步开始和同步结束。 或者,如果只需要单个时间点(事件),则可以将单个同步事件(通常为同步开始)传输到外设。 同步事件可以与 blanking packets 连接以准确传达行间定时,并避免为每个事件在 LPS 和 HS 之间切换的开销。 但是请注意,将数据线保持在 HS 模式下会产生功率损失。

不需要传统同步/消隐/像素定时的显示模块应以高速突发传输像素数据,然后将总线置于低功耗模式,以降低功耗。 推荐的突发大小是像素的扫描线,可以临时存储在显示模块上的行缓冲区中。

¶2) Color Mode On Command, Data Type = 00 0010 (02h)

Color Mode On 是一个单字节数据包命令(两个字节带有 ECC),它将 Video Mode 显示模块切换到低色彩模式以节省电量。

¶3) Color Mode Off Command, Data Type = 01 0010 (12h)

Color Mode Off 是一个单字节数据包(两个字节带有 ECC)命令,它将 Video Mode 显示模块从低颜色模式返回到正常显示操作。

¶4) Shutdown Peripheral Command, Data Type = 10 0010 (22h)

Shutdown Peripheral 命令是一个两字节的数据包(一个命令字节,一个 ECC 字节),用于关闭视频模式显示模块中的显示以节省电量。 请注意,接口应保持通电以接收开启或唤醒命令。

¶5) Turn On Peripheral Command, Data Type = 11 0010 (32h)

打开外设命令是一个单字节数据包(带有 ECC 的两个字节),用于打开视频模式显示模块中的显示器以进行正常显示操作。

¶6) Generic Short WRITE Packet, 0 to 7 Parameters, Data Type = xx x011 (x3h and xBh)

通用短写命令是一种短包类型,用于将通用数据发送到外设。 该数据包内容的格式和解释超出了本规范的范围。 系统设计人员有责任确保主机处理器和外设就此类数据的格式和解释达成一致。

完整的数据包可能长达九个字节,包括一个 ECC 字节。 超出标头 (DI) 字节的字节数由 3 位字段 DT[5:3] 明确指定

¶7) Generic READ Request, 0 to 7 Parameters, Data Type = xx x100 (x4h and xCh)

通用读请求是一个短包,从外设请求数据。 这个包的参数和返回数据的格式和解释超出了本规范的范围。 系统设计人员有责任确保主机处理器和外设就此类数据的格式和解释达成一致。

¶11) Video Mode Interface Timing

视频模式外设需要实时传输像素数据。 本节规定了此类显示模块的 DSI 流量的格式和时序

处理器应支持本节中的所有流量序列。 视频模式外围设备应至少支持本节中的流量序列之一。 外围设备不应要求任何有关流量序列或数据包定时的附加约束。 外设供应商应记录表 19 中列出的所有相关时序参数。

在下图中,BLLP 被定义为视频数据包(例如像素流和同步事件数据包)不会主动传输到外围设备的时间段。

要启用 PHY 同步,主机处理器应定期结束 HS 传输并将数据通道驱动到 LP 状态。 这种转换应该每帧至少发生一次; 在本节的图中显示为 LPM。 建议在水平消隐时间内每条扫描线返回 LP 状态一次。 无论 BLLP 周期的频率如何,主机处理器都负责满足所有记录在案的外设时序要求。 请注意,在较低频率下, BLLP 周期将接近或变为零,并且突发模式将与非突发模式无法区分。

在 BLLP 期间,DSI Link 可以执行以下任何操作:

- 保持空闲模式,LP-RX 主机处理器为 LP-11 状态和 LP-RX

- 使用转义模式将一个或多个非视频数据包从主机处理器传输到外设

- 使用 HS 模式将从处理器向外围设备发送一个或多个非视频数据包

- 如果之前的处理器到外设传输以 BTA 结束,则使用转义模式将一个或多个数据包从外设传输到处理器

- 使用不同的虚拟通道 ID 在 HS 模式下将一个或多个数据包从主机处理器传输到不同的外设